# **CPU** Profile

| Document Number:   | DCIM1041      |

|--------------------|---------------|

| Document Type:     | Specification |

| Document Status:   | Published     |

| Document Language: | E             |

| Date:              | 2017-06-20    |

| Version:           | 4.0.0         |

|                    |               |

Version 4.0.0

**D&LL**EMC

This profile is for informational purposes only and may contain typographical errors and technical inaccuracies. The content is provided as-is, without express or implied warranties of any kind. If there is no separate agreement between you and Dell with regard to feedback to Dell on this profile specification, you agree any feedback you provide to Dell regarding this profile specification will be owned and can be freely used by Dell.

Copyright © 2017 Dell Inc. or its subsidiaries. All rights reserved. Dell, EMC, and other trademarks are trademarks of Dell Inc. or its subsidiaries. Other trademarks may be trademarks of their respective owners.

# Contents

| 1.  | Scope                                              | 4  |

|-----|----------------------------------------------------|----|

| 2.  | Normative References                               | 4  |

| 3.  | Terms and Definitions                              | 4  |

|     | 3.1. Conditional                                   | 4  |

|     | 3.2. Mandatory                                     | 4  |

|     | 3.3. May                                           | 4  |

|     | 3.4. Optional                                      | 4  |

|     | 3.5. Referencing profile                           | 4  |

|     | 3.6. Shall                                         | 5  |

|     | 3.7. FQDD                                          | 5  |

|     | 3.8. Interop Namespace                             | 5  |

|     | 3.9. Implementation Namespace                      | 5  |

|     | 3.10. ENUMERATE                                    | 5  |

|     | 3.11. GET                                          | 5  |

| 4.  | Symbols and Abbreviated Terms                      | 5  |

|     | 4.1. CIM                                           | 5  |

|     | 4.2. iDRAC                                         | 5  |

|     | 4.3. CMC                                           | 5  |

|     | 4.4. WBEM                                          | 5  |

| 5.  | Synopsis                                           | 5  |

| 6.  | Description                                        | 6  |

| 7.  | Implementation Description                         | 7  |

|     | 7.1. CPU View — DCIM_CPUView                       | 8  |

|     | 7.1.1. Resource URIs for WinRM <sup>®</sup>        | 8  |

|     | 7.1.2. Operations                                  | 8  |

|     | 7.1.3. Properties<br>7.2. CPU Profile Registration | 15 |

|     | 7.2.1. Resource URIs for WinRM <sup>®</sup>        | 15 |

|     | 7.2.2. Operations                                  | 15 |

|     | 7.2.3. Properties                                  | 15 |

| 8.  | Methods                                            | 16 |

| 9.  | Use Cases                                          | 16 |

| 10. | CIM Elements                                       | 16 |

| 11. | Privilege and License Requirement                  | 16 |

# 1. Scope

The DCIM CPU Profile describes the properties and interfaces for executing system management tasks related to the management of processors within a system. The profile standardizes and aggregates the description for the CPU properties into a CPU view representation as well as provides static methodology for the clients to query the CPU views without substantial traversal of the model.

# 2. Normative References

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

- DMTF DSP1033, Profile Registration Profile 1.0.0 Dell Lifecycle Controller Best Practices Guide 1.0, <u>http://en.community.dell.com/techcenter/extras/m/white\_papers/20066173.aspx</u>

- Dell WSMAN Licenses and Privileges 1.0

- DMTF DSP0226, Web Services for Management (WSManagement) Specification 1.1.0

- DMTF DSP0227, WSManagement CIM Binding Specification 1.0.0

- Dell Tech Center MOF Library <a href="http://www.delltechcenter.com/page/DCIM.Library.MOF">http://www.delltechcenter.com/page/DCIM.Library.MOF</a>

- DCIM\_CPUView.mof

- o DCIM\_LCEnumeration.mof

- o DCIM\_LCRegisteredProfile.mof

# 3. Terms and Definitions

For the purposes of this document, the following terms and definitions apply.

### 3.1. Conditional

Indicates requirements to be followed strictly in order to conform to the document when the specified conditions are met

## 3.2. Mandatory

Indicates requirements to be followed strictly in order to conform to the document and from which no deviation is permitted

## 3.3. May

Indicates a course of action permissible within the limits of the document

## 3.4. Optional

Indicates a course of action permissible within the limits of the document

## 3.5. Referencing profile

Indicates a profile that owns the definition of this class and can include a reference to this profile in its "Related Profiles" table

# 3.6. Shall

Indicates requirements to be followed strictly in order to conform to the document and from which no deviation is permitted.

# 3.7. FQDD

Fully Qualified Device Descriptor is used to identify a particular component in a system.

# 3.8. Interop Namespace

Interop Namespace is where instrumentation instantiates classes to advertise its capabilities for client discovery.

## 3.9. Implementation Namespace

Implementation Namespace is where instrumentation instantiates classes relevant to executing core management tasks.

# 3.10. ENUMERATE

Refers to WSMAN ENUMERATE operation as described in Section 8.2 of DSP0226\_V1.1 and Section 9.1 of DSP0227\_V1.0

# 3.11. GET

Refers to WSMAN GET operation as defined in Section 7.3 of DSP00226\_V1.1 and Section 7.1 of DSP0227\_V1.0

# 4. Symbols and Abbreviated Terms

## 4.1. CIM

Common Information Model

### 4.2. iDRAC

Integrated Dell Remote Access Controller - management controller for blades and monolithic servers

### 4.3. CMC

Chassis Manager Controller - management controller for the modular chassis

### 4.4. WBEM

Web-Based Enterprise Management

# 5. Synopsis

Profile Name: CPU Version: 4.0.0 Organization: Dell CIM Schema Version: 2.41 Final Dell Schema Version: 1.0.0 Interop Namespace: root/interop

Implementation Namespace: root/dcim

Central Class: DCIM\_CPUView

Scoping Class: DCIM\_ComputerSystem

The Dell CPU Profile is a component profile that contains the Dell specific implementation requirements for CPU view.

DCIM\_CPUView shall be the Central Class.

Table 1 identifies profiles that are related to this profile.

Table 1. Related Profiles

| Profile Name         | Organization | Version | Relationship |

|----------------------|--------------|---------|--------------|

| Profile Registration | DCIM         | 1.0     | Reference    |

# 6. Description

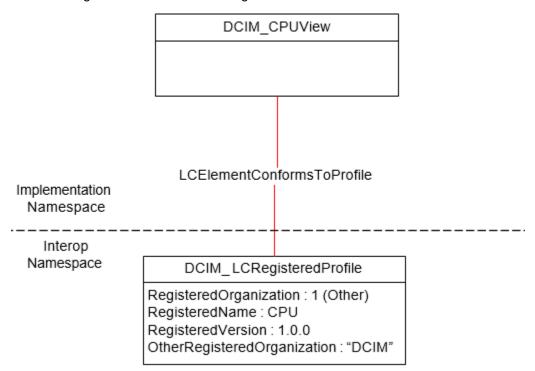

The Dell CPU Profile describes platform's CPUs. Each CPU's information is represented by an instance of DCIM\_CPUView class. Figure 1 details the class diagram of the Dell CPU Profile.

#### Figure 1. Class Diagram

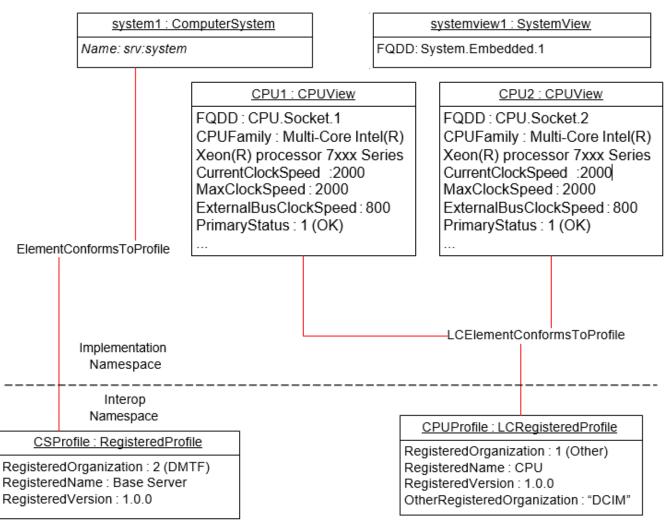

Figure 2 details typical Dell CPU Profile implementation for a platform containing two CPUs. In order fo client to discover the instrumentation's support of this profile, CPUProfile is instantiated in the Interop Namespace. CPUProfile instance describes the information about the implemented profile: most importantly, the name and version of the profile and the organization name that produced the profile.

CPU1 and CPU2 are the CPU views representing the two CPUs in the Implementation Namespace. They are associated to the Interop namespace's CPUProfile instance.

# 7. Implementation Description

This section describes the requirements and guidelines for implementing Dell CPU Profile.

| Element Name                    | Requirement | Description                                                                      |

|---------------------------------|-------------|----------------------------------------------------------------------------------|

| Classes                         | l           |                                                                                  |

| DCIM_CPUView                    | Wandatory   | The class shall be implemented in the Implementation Namespace. See section 7.1. |

| DCIM_LCElementConformsToProfile | Mandatory   | The class shall be implemented in the Implementation Namespace.                  |

| DCIM_LCElementConformsToProfile | Mandatory   | The class shall be implemented in the Interop<br>Namespace.                      |

Table 2.

Class Requirements: CPU Profile

| Element Name                 | Requirement | Description                                                                  |

|------------------------------|-------------|------------------------------------------------------------------------------|

| DCIM_LCRegisteredProfile     | Mandatory   | The class shall be implemented in the Interop<br>Namespace. See section 7.2. |

| Indications                  |             |                                                                              |

| None defined in this profile |             |                                                                              |

# 7.1. CPU View — DCIM\_CPUView

This section describes the implementation for the DCIM\_CPUView class. This class shall be instantiated in the Implementation Namespace.

The DCIM\_LCElementConformsToProfile association(s) shall reference the DCIM\_CPUView instance(s).

Note:- DCIM\_CPUView gives the static inventory of CPUs. For real time status of CPUs, refer to DCIM\_Sensor class.

#### 7.1.1. Resource URIs for WinRM<sup>®</sup>

The class Resource URI shall be "http://schemas.dell.com/wbem/wscim/1/cim-schema/2/DCIM\_CPUView?\_\_cimnamespace=root/dcim"

The key property shall be the InstanceID.

The instance Resource URI for DCIM\_CPUView instance shall be: "http://schemas.dell.com/wbem/wscim/1/cim-schema/2/DCIM\_CPUView?\_\_\_cimnamespace=root/dcim+InstanceID=<FQDD>"

#### 7.1.2. Operations

The following table details the implemented operations on DCIM\_CPUView.

#### **Table 3.**DCIM\_CPUView - Operations

| Operation Name | Requirements | Required Input |

|----------------|--------------|----------------|

| Get            | Mandatory    | Instance URI   |

| Enumerate      | Mandatory    | Class URI      |

#### 7.1.3. Properties

The following table details the implemented properties for DCIM\_CPUView instance representing a processor in a system. The "Requirements" column shall denote the implementation requirement for the corresponding property. If the column "Property Name" matches the property name, the property either shall have the value denoted in the corresponding column "Additional Requirement", or shall be implemented according to the requirements in the corresponding column "Additional Requirement".

#### Table 4.DCIM\_CPUView - Properties

| Property Name          | Requirements | sType  | Requirement and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache1Associativity    | Mandatory    | uint16 | <ul> <li>An integer enumeration defining the system cache associativity:</li> <li>"1" - "Unknown",</li> <li>"2" - "Other",</li> <li>"3" - "Direct Mapped"</li> <li>"4" - "2-way Set-Associative", "5" - "4-way Set-Associative", "6" - "Fully Associative",</li> <li>"7" - "8-way Set-Associative", "8" - "16-way Set-Associative", "10" - "24-way Set-Associative", "11" - "32-way Set-Associative", "12" - "48-way Set-Associative", "13" - "64-way Set-Associative" "14" - "20-way Set-Associative"</li> </ul> |

| Cache1ErrorMethodology | Optional     | uint16 | Cache ErrorMethodology - Contains the enumerated value that<br>describes the cache's error detection/correction mechanism<br>• "1" – Other<br>• "2" – Unknown<br>• "3" – None<br>• "4" – Parity<br>• "5" - Single-bit ECC<br>• "6" Multi-bit ECC                                                                                                                                                                                                                                                                  |

| Cache1Level            | Mandatory    | uint16 | The cache level for Cache1 labeled cache.<br>• "0" – L1<br>• "1" – L2<br>• "2" – L3<br>• "3" –L4<br>• "4" – L5<br>• "5" –L6<br>• "6" – L7<br>• "7" –L8                                                                                                                                                                                                                                                                                                                                                            |

| Cache1PrimaryStatus    | Mandatory    | uint32 | Cache1PrimaryStatus provides a high level status value,<br>intended to align with Red- Yellow-Green type representation<br>of status.<br>• "0" – Unknown<br>• "1" – OK<br>• "2" – Degraded<br>• "3" – Error<br>• "0x8000" - DMTF Reserved<br>• "0xFFFF" - Vendor Reserved                                                                                                                                                                                                                                         |

| Cache1Size             | Mandatory    | uint64 | The property shall represent the total memory size of the cache in KBytes.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Property Name          | Requirements | Туре   | Requirement and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache1SRAMType         | Mandatory    | uint16 | Cache SRAM Type.<br>• "1" – Other<br>• "2" – Unknown<br>• "4" Non-Burst<br>• "8" – Burst<br>• "16" Pipeline Burst<br>• "32" – Synchronous<br>• "64" Asynchronous                                                                                                                                                                                                                                                                                                                                                  |

| Cache1Type             | Mandatory    | uint16 | Defines whether this is for instruction caching (value=3), data<br>caching (value=4) or both (value=5, \"Unified\"). Also, \"Other\"<br>(1) and<br>\"Unknown\" (2) can be defined.                                                                                                                                                                                                                                                                                                                                |

| Cache1WritePolicy      | Mandatory    | uint16 | Defines whether this is write-back (value=1) or write-through<br>(value=0) Cache, or whether this information \"Varies with<br>Address\" (2) or<br>\"Unknown\" (3) can be specified.                                                                                                                                                                                                                                                                                                                              |

| Cache1Location         | Mandatory    | uint8  | Specifies the location of cache <ul> <li>Internal</li> <li>External</li> <li>Reserved</li> <li>Unknown</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |

| Cache2Associativity    | Mandatory    | uint16 | <ul> <li>An integer enumeration defining the system cache associativity:</li> <li>"1" - "Unknown",</li> <li>"2" - "Other",</li> <li>"3" - "Direct Mapped"</li> <li>"4" - "2-way Set-Associative", "5" - "4-way Set-Associative", "6" - "Fully Associative",</li> <li>"7" - "8-way Set-Associative", "8" - "16-way Set-Associative", "9" - "12-way Set-Associative", "10" - "24-way Set-Associative", "11" - "32-way Set-Associative", "12" - "48-way Set-Associative", "13" - "64-way Set-Associative"</li> </ul> |

| Cache2ErrorMethodology | Optional     | uint16 | Cache ErrorMethodology - Contains the enumerated value that<br>describes the cache's error detection/correction mechanism<br>• "1" – other<br>• "2" – Unknown<br>• "3" – None<br>• "4" – Parity<br>• "5" Single-bit ECC<br>• "6" - Multi-bit ECC                                                                                                                                                                                                                                                                  |

| Property Name       | Requirements | Туре   | Requirement and Description                                                                                                                                                                                                                                               |

|---------------------|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache2Level         | Mandatory    | uint16 | The cache level for Cache2 labeled cache.<br>• "0" – L1<br>• "1" – L2<br>• "2" – L3<br>• "3" –L4<br>• "4" – L5<br>• "5" –L6<br>• "6" – L7<br>• "7" –L8                                                                                                                    |

| Cache2PrimaryStatus | Mandatory    | uint32 | Cache2PrimaryStatus provides a high level status value,<br>intended to align with Red- Yellow-Green type representation<br>of status.<br>• "0" – Unknown<br>• "1" – OK<br>• "2" – Degraded<br>• "3" – Error<br>• "0x8000" - DMTF Reserved<br>• "0xFFFF" - Vendor Reserved |

| Cache2Size          | Mandatory    | uint64 | The property shall represent the total memory size of the cache in KBytes.                                                                                                                                                                                                |

| Cache2SRAMType      | Mandatory    | uint16 | Cache SRAM Type.<br>• "1" – Other<br>• "2" – Unknown<br>• "4" Non-Burst<br>• "8" – Burst<br>• "16" Pipeline Burst<br>• "32" – Synchronous                                                                                                                                 |

| Cache2Type          | Mandatory    | uint16 | Defines whether this is for instruction caching (value=3), data caching (value=4) or both (value=5, \"Unified\"). Also, \"Other\" (1) and \"Unknown\" (2) can be defined.                                                                                                 |

| Cache2WritePolicy   | Mandatory    | uint16 | Defines whether this is write-back (value=1) or write-through<br>(value=0) Cache, or whether this information \"Varies with<br>Address\" (2) or \"Unknown\" (3) can be specified.                                                                                         |

| Cache2Location      | Mandatory    | uint8  | Specifies the location of cache <ul> <li>Internal</li> <li>External</li> <li>Reserved</li> <li>Unknown</li> </ul>                                                                                                                                                         |

| Property Name          | Requirements | Туре   | Requirement and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache3Associativity    | Mandatory    | uint16 | <ul> <li>An integer enumeration defining the system cache associativity:</li> <li>"1" - "Unknown",</li> <li>"2" - "Other",</li> <li>"3" - "Direct Mapped"</li> <li>"4" - "2-way Set-Associative", "5" - "4-way Set-Associative", "6" - "Fully Associative",</li> <li>"7" - "8-way Set-Associative", "8" - "16-way Set-Associative", "10" - "24-way Set-Associative", "11" - "32-way Set-Associative", "12" - "48-way Set-Associative", "13" - "64-way Set-Associative"</li> </ul> |

| Cache3ErrorMethodology | Optional     | uint16 | Cache ErrorMethodology - Contains the enumerated value that<br>describes the cache's error detection/correction mechanism.<br>• "1" – other<br>• "2" – Unknown<br>• "3" – None<br>• "4" – Parity<br>• "5" Single-bit ECC<br>• "6" - Multi-bit ECC                                                                                                                                                                                                                                 |

| Cache3Level            | Mandatory    | uint16 | The cache level for Cache3 labeled cache.<br>• "0" – L1<br>• "1" – L2<br>• "2" – L3<br>• "3" –L4<br>• "4" – L5<br>• "5" –L6<br>• "6" – L7<br>• "7" –L8                                                                                                                                                                                                                                                                                                                            |

| Cache3PrimaryStatus    | Mandatory    | uint32 | Cache3PrimaryStatus provides a high level status value,<br>intended to align with Red- Yellow-Green type representation<br>of status.<br>• "0" – Unknown<br>• "1" – OK<br>• "2" – Degraded<br>• "3" – Error<br>• "0x8000" - DMTF Reserved<br>• "0xFFFF" - Vendor Reserved                                                                                                                                                                                                         |

| Cache3Size             | Mandatory    | uint64 | The property shall represent the total memory size of the cache in KBytes.                                                                                                                                                                                                                                                                                                                                                                                                        |

| Property Name         | Requirements | Туре   | Requirement and Description                                                                                                                                                                                                                                                             |

|-----------------------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache3SRAMType        | Mandatory    | uint16 | Cache SRAM Type.<br>• "1" – Other<br>• "2" – Unknown<br>• "4" Non-Burst<br>• "8" – Burst<br>• "16" Pipeline Burst<br>• "32" – Synchronous                                                                                                                                               |

| Cache3Type            | Mandatory    | uint16 | Defines whether this is for instruction caching (value=3), data<br>caching (value=4) or both (value=5, \"Unified\"). Also, \"Other\"<br>(1) and \"Unknown\" (2) can be defined.                                                                                                         |

| Cache3WritePolicy     | Mandatory    | uint16 | Defines whether this is write-back (value=1) or write-through<br>(value=0) Cache, or whether this information \"Varies with<br>Address\" (2) or \"Unknown\" (3) can be specified.                                                                                                       |

| Cache3Location        | Mandatory    | uint8  | Specifies the location of cache <ul> <li>0-Internal</li> <li>External</li> <li>Reserved</li> <li>Unknown</li> </ul>                                                                                                                                                                     |

| Characteristics       | Mandatory    | uint32 | <ul> <li>The characteristics include certain features of the processor such as 64 bit support for data width of the processor.</li> <li>"2" – Unknown</li> <li>"4" - 64-bit Capable</li> </ul>                                                                                          |

| CPUFamily             | Mandatory    | string | The property shall represent processor family type in hexadecimals.                                                                                                                                                                                                                     |

| CPUStatus             | Mandatory    | uint16 | Indicates the current status of the Processor. For example, the<br>Processor might be disabled due to a POST error (value=3).<br>• "0" – Unknown<br>• "1" - CPU Enabled<br>• "2" - CPU Disabled by User<br>• "3" - CPU Disabled By BIOS (POST Error)<br>• "4" - CPU Is Idle "7" - Other |

| CurrentClockSpeed     | Mandatory    | uint32 | The property value shall be in MHz. The current speed (in MHz) of this Processor.                                                                                                                                                                                                       |

| ExternalBusClockSpeed | Mandatory    | uint32 | The property value shall be in MHz. The speed (in MHz) of the external bus interface (known as the front side bus).                                                                                                                                                                     |

| FQDD                  | Mandatory    | string | A string containing the Fully Qualified Device Description, a user-friendly name for the object.                                                                                                                                                                                        |

| InstanceID            | Mandatory    | string | The property value shall be the FQDD property value.                                                                                                                                                                                                                                    |

| DeviceDescription     | Mandatory    | string | A string containing the friendly Fully Qualified Device<br>Description,a property that describes the device and its<br>location                                                                                                                                                         |

| Property Name                       | Requirements | Туре   | Requirement and Description                                                                                                                                                                                                                                                                               |

|-------------------------------------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer                        | Mandatory    | string | The name of the organization responsible for producing the processor.                                                                                                                                                                                                                                     |

| MaxClockSpeed                       | Mandatory    | uint32 | The property value shall be in MHz. The maximum speed (in MHz) of this Processor.                                                                                                                                                                                                                         |

| Model                               | Mandatory    | string | The make and or model of the product                                                                                                                                                                                                                                                                      |

| NumberofEnabledCores                | Mandatory    | uint32 | Number of processor cores enabled for processor.                                                                                                                                                                                                                                                          |

| NumberofEnabledThreads              | Mandatory    | uint32 | Total number of hardware enabled threads for processor.<br>NOTE: The disabling of the multithreading by the BIOS does<br>not affect the number of hardware enabled threads reported by<br>this property.                                                                                                  |

| NumberOfProcessorCores              | Mandatory    | uint32 | Number of processor cores available for processor.                                                                                                                                                                                                                                                        |

| HyperThreadingEnabled               | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| HyperThreadingCapable               | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| VirtualizationTechnologyE<br>nabled | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| VirtualizationTechnologyC<br>apable | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| ExecuteDisabledEnabled              | Mandatory    | uint8  | <ul> <li>0-No</li> <li>1-Yes</li> <li>2 Not Applicable</li> </ul>                                                                                                                                                                                                                                         |

| ExecuteDisabledCapable              | Mandatory    | uint8  | <ul><li>0-No</li><li>1-Yes</li></ul>                                                                                                                                                                                                                                                                      |

| TurboModeEnabled                    | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| TurboModeCapable                    | Mandatory    | uint8  | • 0-No<br>• 1-Yes                                                                                                                                                                                                                                                                                         |

| PrimaryStatus                       | Mandatory    | uint32 | <ul> <li>PrimaryStatus provides a high level status value, intended to align with Red-Yellow- Green type representation of status.</li> <li>"0" – Unknown</li> <li>"1" – OK</li> <li>"2" – Degraded</li> <li>"3" – Error</li> <li>"0x8000" - DMTF Reserved</li> <li>"0xFFFF" - Vendor Reserved</li> </ul> |

| Voltage                             | Mandatory    | string | The property shall represent the voltage(s) of the processor in Volts.                                                                                                                                                                                                                                    |

| Property Name           | RequirementsType |        | Requirement and Description                                                                                                                              |  |

|-------------------------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LastSystemInventoryTime | Mandatory        | string | This property provides the last time \"System<br>\"Inventory Collection On Reboot(CSIOR)\" was performed.<br>The value is represented as yyyymmddHHMMSS. |  |

| LastUpdateTime          | Mandatory        | string | This property provides the last time the data was updated. The value is represented as yyyymmddHHMMSS                                                    |  |

# 7.2. CPU Profile Registration

This section describes the implementation for the DCIM\_LCRegisteredProfile class. This class shall be instantiated in the Interop Namespace.

The DCIM\_LCElementConformsToProfile association(s) shall reference the DCIM\_LCRegisteredProfile instance.

#### 7.2.1. Resource URIs for WinRM<sup>®</sup>

The class Resource URI shall be "http://schemas.dmtf.org/wbem/wscim/1/cimschema/2/CIM\_RegisteredProfile?\_\_cimnamespace=root/interop"

The key property shall be the InstanceID property.

The instance Resource URI shall be: "http://schemas.dell.com/wbem/wscim/1/cim-schema/2/DCIM\_LCRegisteredProfile? cimnamespace=root/interop+InstanceID=DCIM:CPU:1.0.0"

#### 7.2.2. Operations

The following table details the implemented operations on DCIM\_LCRegisteredProfile.

| Table 5.         DCIM_LCRegisteredProfile - Operations |  |

|--------------------------------------------------------|--|

|--------------------------------------------------------|--|

| Operation Name | Requirements | Required Input |  |

|----------------|--------------|----------------|--|

| Get            | Mandatory    | Instance URI   |  |

| Enumerate      | Mandatory    | Class URI      |  |

#### 7.2.3. Properties

The following table details the implemented properties for DCIM\_LCRegisteredProfile instance representing CPU Profile implementation. The "Requirements" column shall denote the implementation requirement for the corresponding property. If the column "Name" matches the property name, the property either shall have the value denoted in the corresponding column "Additional Requirements", or shall be implemented according to the requirements in the corresponding column "Additional Requirements".

| Table 6. | DCIM_LCRegisteredProfile |

|----------|--------------------------|

|----------|--------------------------|

| Property Name               | Requirement | Туре   | Additional Requirements                        |

|-----------------------------|-------------|--------|------------------------------------------------|

| InstanceID                  | Mandatory   | String | DCIM:CPU:4.0.0                                 |

| RegisteredName              | Mandatory   | String | This property shall have a value of "CPU".     |

| RegisteredVersion           | Mandatory   | String | This property shall have a value of "4.0.0".   |

| RegisteredOrganization      | Mandatory   | Uint16 | This property shall have a value of 1 (Other). |

| OtherRegisteredOrganization | Mandatory   | String | The property value shall match "DCIM".         |

| Property Name                 | Requirement | Туре   | Additional Requirements                                                                                                                                                                                                                                                                                             |  |

|-------------------------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AdvertisedTypes[]             | Mandatory   | Uint16 | This property array shall contain [1(Other), 1 (Other)].                                                                                                                                                                                                                                                            |  |

| AdvertiseTypeDescriptions[]   | Mandatory   | String | This property array shall contain ["WS- Identify", "Interop Namespace"].                                                                                                                                                                                                                                            |  |

| ProfileRequireLicense[]       | Mandatory   | String | This property array shall describe the required licenses for<br>this profile.<br>If no license is required for the profile, the property shall<br>have value NULL.                                                                                                                                                  |  |

| ProfileRequireLicenseStatus[] | Mandatory   | String | This property array shall contain the status for the<br>corresponding license in the same element index of the<br>ProfileRequireLicense array property. Each array eleme<br>shall contain:<br>• "LICENSED"<br>• "NOT_LICENSED"<br>If no license is required for the profile, the property shall<br>have value NULL. |  |

# 8. Methods

This section details the requirements for supporting extrinsic methods for the CIM elements defined by this profile. No additional details specified.

# 9. Use Cases

See Lifecycle Controller (LC) Integration Best Practices Guide.

# 10. CIM Elements

No additional details specified.

# 11. Privilege and License Requirement

The following table describes the privilege and license requirements for the listed operations. For the detailed explanation of the privileges and licenses, refer to the Dell WSMAN Licenses and Privileges specification.

| Table 7. | Privilege and License Req | uirements |

|----------|---------------------------|-----------|

|          |                           |           |

| Class and Method                | Operation      | User Privilege Required | License Required               |

|---------------------------------|----------------|-------------------------|--------------------------------|

| DCIM_CPUView                    | ENUMERATE, GET | login                   | LM_REMOTE_ASSET_<br>IN VENTORY |

| DCIM_LCElementConformsToProfile | ENUMERATE, GET | Login                   | None.                          |

| DCIM_LCRegisteredProfile        | ENUMERATE, GET | Login                   | None.                          |